Pamięci masowe z punktu widzenia użytkownika po prostu przechowują one pliki, natomiast z technicznego punktu widzenia, przechowują one dane w sektorach typowo wielkości 512 B. Można powiedzieć, że MSD są „adresowane sektorami”.

W NAND Flash, które stanowią pamięć danych, funkcjonuje zupełnie inny schemat adresowania niż w MSD. Dane są zapisywane i odczytywane stronami o wielkości 2…16 kB, a zapis wymaga uprzedniego wykasowania bloku zawierającego setki stron. Cechy te sprawiają, że w MSD występuje pewne wzmocnienie zapisu (WAF –Write Amplification Factor), uzależnione od aplikacji użytkowania. Ponadto, w niektórych zastosowaniach brak wsparcia dla komendy TRIM powoduje tzw. „garbage collection”.

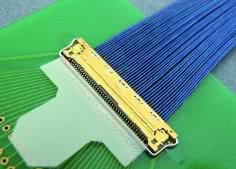

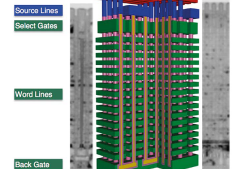

Ze względu na małą cenę i dużą pojemność, pamięci NAND Flash (pat. US20110128788 A1) są powszechnie stosowane jako pamięć danych w MSD. Duża pojemność i niska cena wynikają z ich budowy. Komórki pamięci połączone są w łańcuchy, kilkanaście – kilkadziesiąt tysięcy łańcuchów tworzy stronę. Kilkadziesiąt do kilkaset stron tworzy blok (rysunek 1). W tak utworzonym bloku, komórki pamięci znajdują się na przecięciach linii kolumn BL (Bit Line) oraz wierszy WL (Word Line), dzięki czemu jest możliwe ich duże upakowanie na relatywnie niewielkim obszarze płytki krzemowej. Innym czynnikiem mającym wpływ na cenę i pojemność jest możliwość zapisu wielu bitów informacji w pojedynczej komórce pamięci tj. SLC – 1 bit, MLC – 2 bity, TLC – 3 bity (pat. US 7443724 B2).

Budowa układu pamięci determinuje sposób adresowania danych (rysunek 2). Więcej na ten temat można znaleźć w dokumencie JESD230B, ONFI spec. 4.0. We współczesnych NAND Flash najmniejszą jednostką pojemności podlegającej programowaniu i odczytowi jest strona o pojemności 2…16 kB. Przed ponownym programowaniem zapisanej strony, należy wykasować wszystkie strony znajdujące się w bloku. Dla przykładu, jeżeli blok ma 256 stron o pojemności 16 kB, to pojedyncza komenda ERASE kasuje blok mieszczący 4 MB danych. Załóżmy scenariusz, w którym zapisujemy tylko jeden 512 bajtowy sektor dysku, następnie wydajemy komendę ATA FLUSH CACHE (spec. T13/1699-D). W najlepszym przypadku zostanie zaprogramowana jedna strona NAND Flash o przykładowej pojemności 16 kB. W ten sposób, w NAND Flash jest programowany obszar 31 razy większy niż wynika to z faktycznych potrzeb – w pewnym uproszczeniu, właśnie ten brak dopasowania rozmiaru sektora do pojemności strony jest odpowiedzialny za powstawanie wzmocnienia zapisu WAF (doc. JESD218).

Konsekwencją implementacji mechanizmu wear leveling jest skłonność MSD do przenoszenia nieaktualnych danych. Wyobraźmy sobie, że w systemie operacyjnym nie jest zaimplementowana komenda TRIM (spec. T13/1699-D, systemy starsze od Windows 7 i Linux kernel 2.4). W takiej sytuacji, system nie informuje SSD, które sektory zostały zwolnione przez usunięte pliki i które można usunąć. Późniejszy wewnętrzny proces defragmentacji przenosi sektory zassane nieaktualnymi danymi w inne obszary NAND Flash zwiększając WAF.

Rozważany przypadek użycia TRIM dotyczy SSD. Karty SD/uSD/MMC mają równoważne polecenie „ERASE” (eMMC również TRIM), które umożliwia wykasowanie grupy sektorów (doc. JESD84, doc. SD Specifications Part 1 Physical Layer Simplified Specification). Gdy system ma możliwość bezpośredniego operowania na interfejsie karty, aplikacja powinna zadbać o kasowanie zwalnianych sektorów. Pamięci typu USB są zupełnie pozbawione tej możliwości. Jeszcze inną możliwość obniżenia WAF daje buforowanie cykli zapisu w pamięci RAM (doc. BPLRU: A buffer management scheme for improving random writes in flash storage). Każdy kontroler MSD ma wbudowaną lub zewnętrznej pamięć RAM. Jest ona używana w celu skompletowania danych, możliwie dobrze wypełniających całą pojemność strony NAND Flash. Zatem buforowanie cykli zapisu w pamięci RAM systemu operacyjnego pozwala na zwiększenie sprawności wbudowanych mechanizmów optymalizacji.

Dzięki zaawansowanym rozwiązaniom wbudowanym w omawiane kontrolery, użytkownik nie musi poświęcać czasu na implementacje własnych mechanizmów optymalizacji, translacji adresów i innych. Należy jednak pamiętać, że budowa MSD musi być dopasowana do aplikacji. Czytelników zachęcamy do zapoznania się z wskazaną literaturą, która w pozwoli na dogłębne zapoznanie się z budową pamięci masowych.

Wilk Elektronik S.A.

Zaloguj

Zaloguj