Jako elementy wykonawcze pracują tranzystory IRF7307 produkcji International Rectifier. W obudowie SO-8 zamknięte zostały dwa tranzystory typu MOSFET: jeden z kanałem P i drugi, z kanałem N. Niektóre ich parametry zostały wymienione w tabeli 1.

Tranzystory te bardzo dobrze nadają się do zastosowania w układach zasilanych niskimi napięciami, przede wszystkim ze względu na napięcie progowe. Dodatkowo, mała rezystancja otwartego kanału poskutkuje niskimi stratami napięcia: obciążenie pobierające prąd 1 A odłoży na tranzystorach mostka nie więcej niż 140 mV przy zasilaniu napięciem 4,5 V, czyli zaledwie 3% całego napięcia zasilania.

Ponadto, zawierają one w swej strukturze szybkie diody, które posłużą zabezpieczeniu tranzystorów przed przebiciem przy przełączaniu obciążeń o charakterze indukcyjnym (np. silników).

Z drugiej zaś strony, tak niska wartość napięcia progowego wymusza, aby napięcie UGS wyłączonego tranzystora było możliwie bliskie zeru - w przeciwnym razie, prąd zacznie płynąć przez obydwa tranzystory źle sterowanej gałęzi mostka; spowoduje to ich nagrzewanie i, w efekcie, spalenie. Na rysunku 1 znajduje się schemat ideowy omawianego układu.

Do sterowania wykorzystane zostały bramki logiczne NAND typu 4093, które zawierają w swej strukturze przerzutnik Schmitta. Maksymalny dropout wyjść tych bramek na poziomie 50 mV (według Texas Instruments) - jest to wartość wystarczająca, aby spowodować całkowite otwarcie lub zatkanie kanałów tranzystorów MOSFET, niezależnie od napięcia sterującego wejście bramki.

W przypadku bramek niezawierających przerzutnika Schmitta, istnieje ryzyko, że napięcie sterujące daną gałęzią ustali się na takiej wartości, że zniszczeniu ulegną tranzystory tej gałęzi oraz źródło zasilania, które zostanie czasowo zwarte.

Dwie nieużywane bramki mają zwarte wejścia dołączone do stałych potencjałów. Oporniki R1 i R2 ustalają potencjał wejść przy niepodłączonym źródle sterującym.

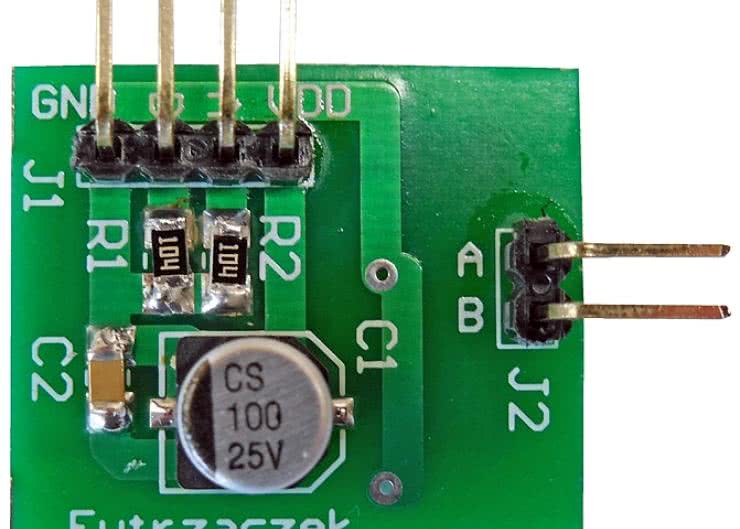

Układ został zmontowany na dwustronnej płytce drukowanej o wymiarach 22×25 mm, której wzór ścieżek widoczny jest na rysunku 2. Nie są wymagane jakiekolwiek czynności uruchomieniowe, układ jest od razu gotowy do pracy.

Napięcie zasilania zawiera się w przedziale 3-12 V i jest restrykcyjnie ograniczone przez maksymalne Hnapięcie UGS tranzystorów mocy. W stanie ustalonym, przy braku jakichkolwiek połączeń (poza zasilaniem), układ pobiera prąd mniejszy niż 1 µA. W układzie modelowym zostały użyte złącza kątowe typu goldpin, aby ograniczyć wysokość modułu.

Ponieważ układ sterujący bramkami tranzystorów ma ograniczoną wydajność prądową (rzędu pojedynczych miliamperów), zmiana stanu wyjścia gałęzi trwa stosunkowo długo. Jest to cena prostoty tego układu. W czasie przełączania bramki CMOS na przeciwny stan logiczny, kanały obydwu tranzystorów są otwarte i pobierają duży prąd ze źródła zasilania. Wynika z tego, że warto przełączać je z możliwie małą częstotliwością, najlepiej nieprzekraczającą kilkuset herców.

Michał Kurzela, EP

Zaloguj

Zaloguj