Wprowadzenie: skok do rozpoczęcia projektowania z programowanymi układami SoC

Dzięki zastosowaniu programowalnych układów scalonych SoC można przyśpieszyć konstruowanie urządzeń, ułatwić ich miniaturyzację oraz ograniczyć pobór mocy w aplikacjach, które wymagają dużej mocy obliczeniowej i krótkiego czasu reakcji. Typowe przykłady obejmują zaawansowane sterowniki napędów, urządzenia telekomunikacyjne, systemy wizyjne oraz platformy machine-learning.

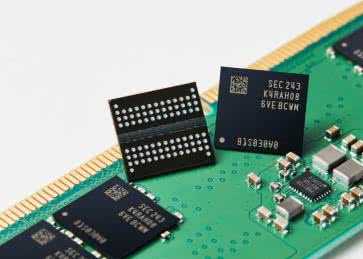

Pomimo niewątpliwych zalet integracji wielu bloków w pojedynczym układzie scalonym SoC opracowanie bazującego na nim systemu nie jest łatwe i obejmuje szereg zagadnień, do których należą zaprojektowanie i wykonanie płytki drukowanej zawierającej szybkie linie interfejsowe, integracja pamięci systemowej i szybkich interfejsów, takich jak Ethernet oraz zarządzanie zasilaniem. Ponadto, zarządzanie zasilaniem staje się bardziej złożone z kolejną generacją programowalnych układów SoC ze względu na wzrost liczby opcji zintegrowanych w układzie oraz rosnące i coraz bardziej rygorystyczne wymagania na poziomie systemu.

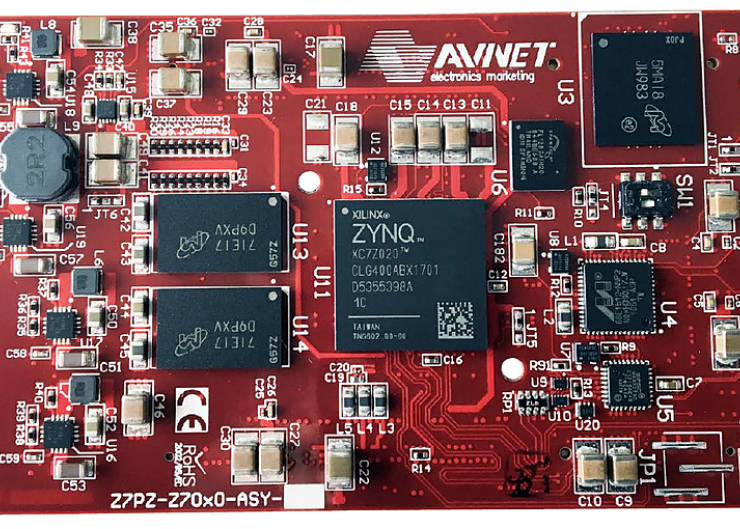

Moduł SoM zawiera układ Xilinx Zynq UltraScale+ – ZU3EG. Moduł ten charakteryzuje się zastosowaniem najnowszej generacji wysoce zintegrowanych, wydajnych, programowalnych układów SoC, które łączą zaawansowaną technologię FPGA z wielordzeniowym systemem procesorowym, szybką zintegrowaną pamięcią i szybkimi interfejsami komunikacyjnymi. Jednak niezależnie od tego, czy używa się ich w module SoM, czy też na tradycyjnej płytce prototypowej z układami FPGA, zapewnienie prawidłowego zasilania tych zróżnicowanych zasobów wiąże się z wieloma wyzwaniami konstrukcyjnymi.

Wyzwania związane z zarządzaniem zasilaniem

Współczesne programowalne układy SoC wymagają wielu szyn zasilających doprowadzających napięcie o różnej wartości. Dodatkowo do napięcia zasilania rdzenia system z układem Zynq ma odrębne domeny zasilające dla zintegrowanych w jego strukturze: pamięci, linii I/O, generatora PLL taktującego pracą P/O oraz bloku SerDes. Pewne opcje, takie jak np. pamięć operacyjna lub tryby obniżonego poboru energii, mogą wymagać nieprzerwanego napięcia zasilającego i dodatkowych jego doprowadzeń, co nie jest bez wpływu na system zasilania. Zależnie od użytego układu SoC (modułu SoM) może być wymagane od 7 do 10 indywidualnych doprowadzeń zasilania, które muszą być załączane i wyłączane z zachowaniem odpowiedniej sekwencji. Firma Infineon opracowała i wprowadziła do oferty systemy zasilania dla układów Zynq UltraScale+ od ZU2 do ZU19 współpracując z firmą Xilinx w zakresie zoptymalizowanej, skonsolidowanej szyny zasilającej opisanej w dokumentach „Xilinx UG583 UltraScale Architecture PCB Design” oraz „Infineon Power Solutions for Xilinx Zynq UltraScale+ MPSoC” w rozdziałach „Always On: Cost Optimized Power Rail Consolidation” i „Always On: Power/Efficiency Rail Consolidation for Low Power Devices”. Rozwiązania firmy Infineon pojawiają się wielokrotnie w różnych notach aplikacyjnych firm Avnet i Xilinx dotyczących układów z rodziny Zynq UltraScale+.

Istnieją dokładne specyfikacje tolerancji wartości napięcia DC i odpowiedzi na zmieniające się skokowo obciążenie. Napięcie zasilające rdzenia dla Zynq UltraScale+ musi być stabilizowane z niepewnością do 1% przy poziomie szumów nieprzekraczającym 10 mVpp. Ponadto, ponieważ układy, takie jak Zynq firmy Xilinx są produkowane z użyciem 16-nanometrowego procesu FinFET, tak dokładne stabilizowanie napięcia jest wymagane już przy napięciu 0,72 V.

Układy z rodziny Zynq UltraScale+ zawierają również bloki interfejsowe SerDes z wyprowadzeniami I/O zapewniającymi efektywną konwersję bardzo szybkich protokołów szeregowych stosowanych do transmisji danych poza układem scalonym na transmisję równoległą wewnątrz SoC, w obrębie bloków IP oraz modułów logicznych. Aktywne bloki SerDes wymagają dodatkowych linii zasilających i narzucają jeszcze większe wymagania odnośnie do odpowiedzi impulsowej. Wymagają one do 20 W mocy zasilania, zależnie od liczby aktywnych modułów oraz typu układu. Mogą pracować z prędkością od 1,5 Gb/s do 80 Gb/s, przy której to poziom szumów występujących na zasilaniu nie może przekraczać 10 mVpp.

Jakby zaprojektowanie zasilacza spełniającego te wszystkie wymagania nie było wystarczająco skomplikowane, potrzebna jest również elastyczność, aby reagować na zmieniające się wymagania, ponieważ często projekt jest korygowany lub skalowany w trakcie realizacji. Jeśli zostanie zmieniony układ SoC, liczba szyn i zużycie energii również zmienia się w zależności od wybranego układu i jego zasobów, które są używane. Na domiar tego, obwody zasilające muszą zajmować niewielką powierzchnię, aby w pełni umożliwić wykorzystanie zalet miniaturyzacji uzyskanych dzięki układowi SoC o dużej skali integracji.

Avnet zdecydował się na użycie dwóch układów PMIC firmy Infineon typu IRPS5401 na płytce swojego modułu SoM UltraZed-EG. Każdy z nich zawiera pięć przetwornic DC/DC oraz jeden regulator LDO (rysunek 2). Dla zapewnienia dodatkowej elastyczności przy zasilaniu rdzenia prądem o natężeniu do 40 A, jeden z kanałów przetwornicy DC/DC ma wyjście PWM, które może być używane do zarządzania zewnętrznym układem stopnia mocy, takim jak TDA21240.

Układ PMIC typu IRPS5401 upraszcza również programowanie prawidłowej sekwencji załączania i wyłączania zasilania. Jest to trudne do wykonania przy projektowaniu zasilacza od przysłowiowego zera. Stosując układ IRPS5401 można szybko zaprogramować odpowiednią sekwencję za pomocą wygodnego w użyciu interfejsu graficznego Infineon PowIRCenter. Czas opóźnienia po włączeniu/wyłączeniu zasilania oraz czas narastania/opadania dla każdej szyny są programowane poprzez zapisanie wymaganych wartości w wewnętrznych rejestrach PMIC (rysunek 4).

Programowanie sekwencji załączania/wyłączania napięcia przez układ IRPS5401 jest znacznie szybsze i łatwiejsze, niż opracowywanie indywidualnych obwodów czasowych dla każdej szyny zasilającej w odrębnie wykonanych obwodach zasilających. Sekwencja napięć jest zapamiętywana wewnątrz PMIC, który pracuje niezależnie, więc nie jest wymagany zewnętrzny mikrokontroler lub timer sekwencjonujący czasy, co oszczędza przestrzeń na płytce PCB i obniża koszt gotowego urządzenia. Układ IRPS5401 zawiera rejestry oraz zintegrowane obwody analogowe służące do stabilizacji napięcia, nie wymagając przy tym stosowania żadnych komponentów zewnętrznych. Inżynierowie mogą wyspecyfikować odpowiednie limity oraz skontrolować marginesy pracując z użyciem oprogramowania PowIRCenter.

Skalowalne zasilanie dla programowalnych układów SoC

Infineon opracował układ IRPS5401 dla zapewnienia skalowalnego rozwiązania dla systemów zasilania wymaganych przez układy FPGA i programowalne układy SoC wytwarzane przez wielu producentów. Może on usprawnić zarządzanie zasilaniem w systemach wykorzystujących układy Zynq UltraScale+, począwszy od podstawowej, najprostszej rodziny ZU2, a skończywszy na wysokowydajnej serii ZU19. Podstawowe linie układów Zynq UltraScale+ CG wyposażone są w dwurdzeniowy procesor ARM Cortex-A53 oraz dwurdzeniowy R5. Bardziej wydajne układy Zynq UltraScale+ EG łączą czterordzeniowy Cortex-A53, dwurdzeniowy R5 z koprocesorem graficznym Mali-400, a rodzina Zynq UltraScale+ EV charakteryzuje się z kolei czterordzeniowym Cortex-A53, dwurdzeniowym R5, Mali-400 i sprzętowym kodekiem video H.264/H.265.

Moduł SoM UltraZed-EG firmy Avnet zawiera pojedynczy układ Zynq UltraScale+ ZU3 EG. Wykorzystano w nim elastyczność IRPS5401 oraz jego wysoką skalę integracji dla osiągnięcia miniaturowych wymiarów – moduł zajmuje powierzchnię o wymiarach zaledwie 3,5 cala×2 cale (76,2 mm×50,8 mm). Użytkownicy SoM mogą korzystać z elastyczności układu PMIC, aby dostroić system zasilania do wymagań aplikacji za pomocą PowIRCenter w miarę rozwoju projektu. Może to zaoszczędzić tygodnie lub miesiące prób i błędów, w przeciwnym razie jest konieczna optymalizacja konwencjonalnego systemu zasilania.

Współczesne układy FPGA o dużej skali integracji i zaawansowane, programowalne układy SoC narzucają nowy trend w kierunku zwiększenia liczby zintegrowanych funkcji, podnosząc wymagania wobec układów zasilających. Wymuszają one zwiększenie liczby torów zasilających i natężenia prądu szczytowego na daną szynę. Jednocześnie wymagają dokładniejszej stabilizacji napięcia oraz wydajniejszej odpowiedzi impulsowej. Kwestie takie, jak gęstość mocy, sekwencjonowanie i skalowalność zasilania stają się coraz bardziej znaczące. Projektowanie zasilacza spełniającego wszystkie te wymagania jest złożonym i wymagającym zadaniem, stając się nie lada wyzwaniem dla konstruktorów.

Konfigurowalny układ PMIC, zaprojektowany specjalnie do zasilania nowoczesnych układów scalonych, stanowi elastyczne i skalowalne rozwiązanie. Okazało się ono kluczowym czynnikiem podczas tworzenia programowalnego modułu UltraZed-EG firmy Avnet, który usprawnia opracowywanie produktów wykorzystujących układy Xilinx Zynq UltraScale+.

Udo Blaga i Tony Ochoa

Avnet Silica

Zaloguj

Zaloguj