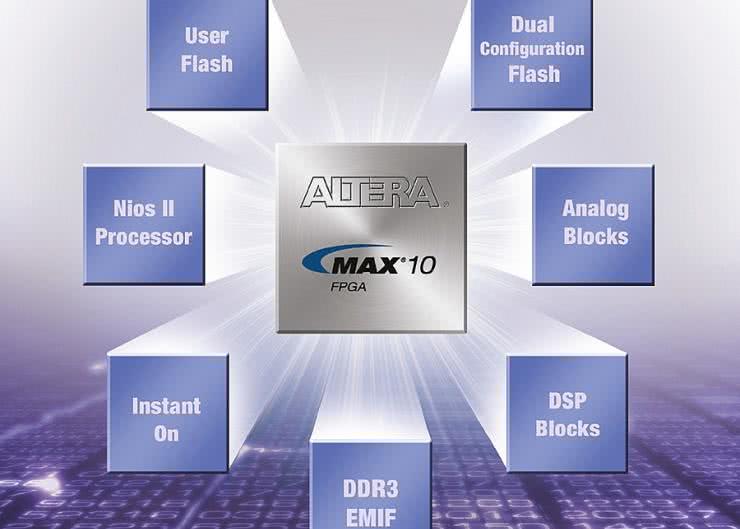

Układy z rodziny MAX10 - pomimo prefiksu sugerującego przynależność do grupy układów CPLD - są nowoczesnymi układami FPGA. Ich architektura bazuje na układach Cyclone IV. Schemat blokowy ją ilustrujący przedstawiono na rysunku 1. O ile budowa układów MAX10 nie wywołuje przyspieszonego bicia serca u konstruktora, to bez wątpienia wywołują je zastosowane w tych układach nowości, na których przede wszystkim skupimy się w artykule.

Po pierwsze, układy MAX10, to pierwsza w ofercie Altery rodzina układów programowalnych FPGA pozbawionych najpoważniejszej - z punktu widzenia "masowych" użytkowników - wady tego typu układów: nie wymagają one zewnętrznej pamięci konfigurującej Flash! Stało się tak dzięki zintegrowaniu pamięci nieulotnej Flash-NOR ze strukturą rekonfigurowalną. Pamięć ta jest podzielona na dwa podstawowe obszary, widoczne na rys. 1:

- Pamięć konfigurującą CFM, w której jest przechowywany obraz konfiguracji FPGA. Większość dostępnych typów układów z serii MAX10 (poza najmniejszymi - patrz tabela 1) wyposażono w dwa banki wewnętrznej pamięci konfiguracyjnej, dzięki czemu można dokonywać błyskawicznej "rekonfiguracji" sprzętu, bez konieczności zatrzymywania pracy całego systemu.

- Pamięć Flash dla aplikacji użytkownika (UFM - User Flash Memory), dostępna w układzie za pośrednictwem magistrali Avalon Memory-Mapped, o maksymalnej pojemności dochodzącej do niemal 6 Mb. Pamięć ta może być używana jako równoległa z taktowaniem do 116 MHz i maksymalnej szerokości słowa 32 bity lub jako szeregowa, z maksymalną częstotliwością taktowania wynoszącą ok. 7,25 MHz.

Obydwie pamięci są podzielone na sektory, które można programować niezależnie od siebie, co zwiększa trwałość pamięci nieulotnej, która i tak jest duża - producent deklaruje minimalna liczbę cykli kasowanie-zapis wynoszącą 10000 w pełnym zakresie temperatur oraz trwałość zapisanych danych nie krótszą niż 20 lat przy temperaturze otoczenia nie wyższej niż +85°C.

Kolejną - rzadko spotykaną w układach PLD atrakcją - są wbudowane w układy MAX10 przetworniki A/C o rozdzielczości 12 bitów (rysunek 2). W zależności od wersji układu i zastosowanej obudowy, są one wyposażone w jeden lub dwa przetworniki ADC (SAR), o łącznej liczbie kanałów wejściowych wynoszącej maksymalnie 18.

Układy są wyposażone w jedno lub dwa dedykowane wejścia analogowe, pozostałe linie wejściowe mogą być wykorzystywane z puli uniwersalnych I/O. Maksymalna częstotliwość próbkowania sygnału analogowego przez A/C wynosi 1 MHz, sygnał taktujący jest generowany przez zdefiniowane przez producenta generatory PLL.

Interesującym zabiegiem producenta, praktycznie niespotykanym w rozwiązaniach konkurencyjnych, jest wyposażenie kanałów wejściowych w programowany dzielnik napięcia, który umożliwia pomiar napięć o wartości dwukrotnie większej, niż napięcie zasilania A/C.

Ponadto, przetwornik wyposażono w półprzewodnikowy (diodowy) czujnik temperatury, który jest dołączony do jednego z wejść przetwornika A/C. Podczas pomiaru temperatury przetwornik domyślnie jest taktowany sygnałem zegarowym o częstotliwości 50 kHz.

Uniwersalne GPIOLinie I/O w układach MAX10 są przystosowane do współpracy z układami cyfrowymi wyposażonymi w styki fizyczne pracujące w jednym z ponad 30 standardów czasowo-napięciowych, obsługiwanych przez układy MAX10 (m.in. HSTL, SSTL, HSUL, LVDS, PPDS, LVPECL, TMDS itd.). Układy MAX10 wyposażono w aktywowane przez użytkownika rezystory terminacyjne (blok OCT - On-Chip Termination), które można wykorzystywać w szybkich interfejsach komunikacyjnych.

|

W układach MAX10 interfejs do pamięci zewnętrznej jest realizowany jako soft IP. Zaznaczone zdanie sugeruje, że jest tam blok hard IP. Ze względu na dużą częstotliwość taktowania interfejsu pamięci zewnętrznej (do 303 MHz w przypadku pamięci DDR3/ DDR3L), producent przewidział możliwość dynamicznej modyfikacji fazy sygnału taktującego, która jest modyfikowana w zależności od napięcia zasilającego i temperatury w taki sposób, aby zminimalizować straty czasu podczas cykli zapisu/odczytu danych.

Oczywiście, nie są to wszystkie cechy i zalety nowych układów firmy Altera, zgodnie z początkową zapowiedzią skupiliśmy się teraz na najważniejszych, zastosowanych w nich nowościach. Nieco więcej informacji na temat praktycznych możliwości układów MAX10 przedstawimy w kolejnych numerach EP, na koniec jeszcze kilka słów na temat zestawów startowych i ewaluacyjnych wyposażonych w nowe układy Altery.

Jednym z najtańszych na rynku (ok. 45 EUR netto) jest zestaw Mpressions Odyssey MAX 10 Evaluation Kit (fotografia 4) wyposażono w układ 10M08SAU169C8GES oraz ekspander z interfejsem radiowym BLE (Bluetooth 4.0), akcelerometrem, czujnikami temperatury i wilgotności oraz sensorem oksymetrycznym umożliwiającym pomiar tętna.

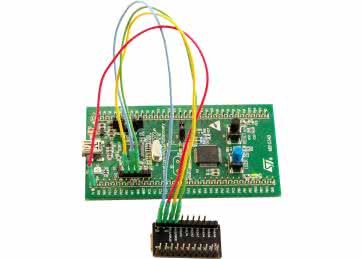

Kolejnym w rankingu cenowym (ok. 50 EUR netto) zestawem z układem z rodziny MAX10 jest Altera MAX 10 Evaluation Kit (fotografia 5). Zastosowano w nim układ w obudowie LQFP144 (10M08SAE144C8GES) w dość skromnym otoczeniu, co jest częściowo rekompensowane przez złącze zgodne z Arduino Rev. 3, dzięki któremu do współpracy z układem MAX10 można użyć dowolnych ekspanderów (shieldów) Arduino, przy czym muszą być one przystosowane do zasilania napięciem 3,3 V. Schemat blokowy tego zestawu pokazano na rysunku 6.

Najlepiej wyposażony zestaw z układem MAX10 jest Altera MAX 10 FPGA Development Kit (fotografia 7). Wyposażono go w największy układ z rodziny - 10M50DAF484C6GES - a także szereg peryferii tworzących z zestawu kompletny komputer z interfejsami komunikacyjnymi Ethernet i USB, niezłym wyposażeniem "pokładowym" oraz możliwością łatwej rozbudowy - dzięki zastosowaniu złącz HSMC i Pmod. Cena tego zestawu nie jest niestety niska - ok. 200 EUR netto - ale nie odbiega od porównywalnych platform ewaluacyjnych dla innych współczesnych układów cyfrowych.

Na tym kończymy ekspresowe wprowadzenie do nowej rodziny układów FPGA firmy Altera, za miesiąc przybliżymy cechy i możliwości zestawu Altera MAX 10 Evaluation Kit, który - po analizie ceny, cech i wyposażenia - jest optymalną platformą sprzętową zarówno do celów ewaluacyjnych jak i realizacji kompleksowych projektów, także bazujących na "miękkich" wersjach 32-bitowych mikroprocesorów.

Piotr Zbysiński, EP

Zaloguj

Zaloguj