Szeroko rozpowszechniona i coraz bardziej zaawansowana technologia CMOS i TTL, która stanowi bazę dla produkcji nowoczesnych układów elektronicznych, jest bardzo wrażliwa na wyładowania elektrostatyczne, określane też mianem zdarzeń ESD.

Powodem powstania wyładowania jest utworzenie się wysokiej różnicy potencjałów w wyniku nagromadzenia się ładunku elektrostatycznego (napięcie, przy którym dojdzie do wyładowania może nawet osiągnąć wartości kilkunastu kV).

Oprócz uszkodzenia wrażliwego przyrządu, nastąpi przepływ prądu o wysokim natężeniu i częstotliwości. Zdarzenie ESD wygeneruje niechcianą falę elektromagnetyczną, która może być źródłem interferencji elektromagnetycznej (EMI).

Indukcja elektromagnetyczna - trochę teorii

U podstaw problemów z kompatybilnością elektromagnetyczną (EMC) stoi zjawisko zwane indukcją elektromagnetyczną. Polega ono na powstaniu siły elektromotorycznej SEM (i w konsekwencji przepływu ładunku) w przewodniku znajdującym się w zmiennym strumieniu indukcji pola elektromagnetycznego ΦB. Wielkość tej siły definiuje prawo indukcji elektromagnetycznej Faraday'a:

| (1) |

gdzie:

SEM - wyindukowana w przewodniku siła elektromagnetyczna. Jej jednostką jest wolt [V];

ΦB - strumień indukcji magnetycznej przepływający przez powierzchnię ograniczoną przewodnikiem;

![]()

Wzór (1), nam elektronikom, może wydawać się nieco "mało atrakcyjny". Jednakże przedstawienie prawa Faraday'a w postaci całki (2), może już nam powiedzieć całkiem sporo.

| (2) |

gdzie:

I - prąd który przepłynie przez przewodnik o długości l i oporze R;

R - opór przewodnika;

![]()

B - indukcja pola magnetycznego;

S - powierzchnia ograniczona przez przewodnik o długości l;

dS - nieskończenie mały wycinek powierzchni S.

Na podstawie wzoru (2) można zauważyć, że natężenie wyindukowanego prądu jest wprost proporcjonalne do:

- indukcji pola magnetycznego oraz szybkości, z którą się ono zmienia,

- powierzchni, jaką ogranicza przewodnik, a więc i długości przewodnika.

Żeby zminimalizować natężenie wyindukowanego prądu, który mógłby negatywnie wpłynąć na funkcjonowanie projektowanego systemu, należałoby więc utrzymać na jak najniższym poziomie wartość indukcji pola magnetycznego i częstotliwość jego zmian oraz unikać tworzenia dużych pętli prądowych.

Jednoczenie należy zwrócić uwagę na fakt, że pole magnetyczne nie tylko dociera ze świata zewnętrznego do projektowanego układu, ale jest również w nim wytwarzane. Zgodnie z prawem Ampere'a, wokół przewodnika, w którym płynie prąd o stałym natężeniu I, jest wytwarzane stałe pole magnetyczne o wartości indukcji magnetycznej B (3).

| (3) |

gdzie:

B - indukcja magnetyczna wytworzonego pola magnetycznego;

dl - nieskończenie mały odcinek linii całkowania C;

µ - przenikalność magnetyczna ośrodka, w którym rozchodzi się pole magnetyczne;

I - natężenie prądu objętego linią całkowania C, który wytwarza pole magnetyczne.

Jeżeli natężenie płynącego przez przewodnik prądu będzie ulegało zmianom, zmieniać się również będzie wartość indukcji pola magnetycznego B. Wynika z tego, że sposobem na uzyskanie pola magnetycznego o jak najmniejszej częstotliwości i indukcji magnetycznej, jest operowanie w zakresie jak najmniejszych natężeń prądów i jak najniższych częstotliwości.

Optymalizacja oporu ścieżki R pod kątem zmniejszenia natężenia wyindukowanego prądu jest nieuzasadniona. Poprzez zwiększenie rezystancji ścieżek pogorszymy również parametry propagacji sygnałów pożądanych.

Źródła niechcianego pola elektromagnetycznego

Jak już wcześniej wspomniałem, źródła szumu elektromagnetycznego mogą znajdować się zarówno w projektowanym systemie, jak i poza jego granicami. Ogólna zasada mówi, że należy rozpocząć odszumianie jak najbliżej miejsca powstawania szumów i jak najdalej od wrażliwych części systemu. Aby tego dokonać, konstruktor musi wiedzieć gdzie należy rozpocząć poszukiwania owych źródeł. Zakłócenia są generowane w układzie zazwyczaj przez:

- źródła sygnałów szybkozmiennych, np. mikrokontroler, oscylator, zasilacz impulsowe, zdarzenie ESD,

- układy pobierające duże ilości prądu, np. wzmacniacz audio, silnik elektryczny,

- przewody i ścieżki, którymi prowadzony jest prąd o dużym natężeniu, i/albo o wysokiej częstotliwości,

- przewody, ścieżki, pola, których wymiary odpowiadają całkowitym wielokrotnościom: l/20, l/4, l/2 prowadzonej fali,

- ścieżki tworzące pętle (działają podobnie do anteny ramowej),

- niepoprawnie umieszczone, długie przewody (zazwyczaj formują antenę dipolową),

- miejsca przerwania powierzchni masy (działają podobnie do anten szczelinowych),

- placki miedzi o niezdefiniowanym potencjale (mają one skłonność do magazynowania i odbijania energii).

W przypadku wymienionych źródeł możliwe jest ich usunięcie bądź podjęcie działań mających na celu zmniejszenie ilości generowanych przez nie zaburzeń. Niestety, z szumami elektromagnetycznymi pochodzącymi spoza układu trzeba radzić sobie w odmienny sposób. Nie jest możliwe wyeliminowanie ich źródła ani też zmniejszenie jego emisyjności, zatem projektowany system musi być na nie odporny.

Na początek należy zdefiniować środowisko elektromagnetyczne, w którym projektowany system będzie pracował i następnie dostosować go do niego. Redukcja zakłóceń powinna rozpocząć się już na etapie linii wejściowych/wyjściowych systemu oraz kabli zasilających. Jeżeli wraz z systemem dostarczamy okablowanie (tj. z monitorem VGA) można już za ich pomocą rozpocząć proces odszumiania. Typowymi strategiami redukcji zakłóceń pochodzenia zewnętrznego są:

- używanie jak najkrótszych kabli zasilających i sygnałowych,

- stosowanie kabli ekranowanych lub skrętek,

- umieszczanie na okablowaniu koralików ferrytowych,

- użycie szczelnego ekranu w celu zmniejszenia dochodzącego do systemu (bądź tylko do wrażliwego podsystemu) promieniowania elektromagnetycznego.

Strategie eliminowania zaburzeń EMI

Działania mające na celu redukcję kłopotów związanych z interferencją elektromagnetyczną powinno rozpocząć się na jak najwcześniejszym etapie projektu. W późniejszych fazach rozwiązywanie pojawiających się problemów z EMC będzie trudniejsze, droższe albo często niemożliwe.

Warto zainwestować już na samym początku wykonywania systemu elektronicznego nieco czasu i środków w stworzenie urządzenia, które będzie bezawaryjnie funkcjonowało w określonym środowisku elektromagnetycznym, nie zakłócając jednocześnie pracy innych sprzętów w nim się znajdujących.

Wykonanie i umieszczenie masy na płytkach n-warstwowych. Bardzo istotne w walce z szumami elektromagnetycznymi jest prawidłowe wykonanie płaszczyzny masy. W wielu projektach płaszczyzna masy jest utworzona przez przypadkowo połączone placki miedzi, znajdujące się w miejscach, w których nie zostały poprowadzone żadne inne ścieżki. Tak wykonana masa nie spełnia swojej roli.

Głównym zadaniem masy jest odprowadzanie prądów zwrotnych. Przepływ jakiegokolwiek rodzaju sygnału (nieważne, czy jest to zasilanie, szum, czy sygnał zegarowy) spowoduje powstanie prądu zwrotnego, płynącego w kierunku źródła sygnału.

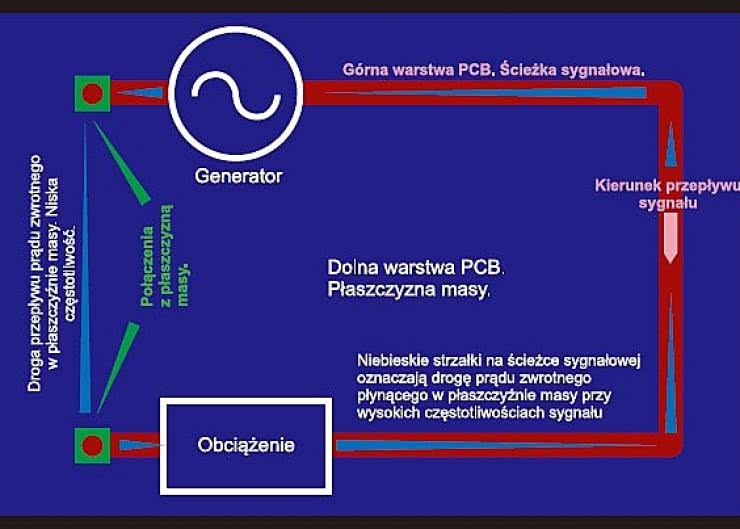

Takie zachowanie jest związane z tym, że prąd płynie w zamkniętych pętlach. Wymuszenie przepływu sygnału ze źródła do odbiornika spowoduje powstanie prądu płynącego w odwrotnym kierunku (rysunek 1). Prąd zwrotny będzie zawsze biegł drogą o najmniejszej impedancji. W przypadku niskich częstotliwości (poniżej 1 MHz) część urojona impedancji (reaktancja) będzie miała niewielki wpływ na moduł impedancji.

Można powiedzieć, że prąd zwrotny o niskiej częstotliwości będzie biegł ścieżką o najmniejszej rezystancji. W przypadku sygnałów o wysokich częstotliwościach reaktancja będzie miała duży wpływ na moduł impedancji. Prąd zwrotny o wysokiej częstotliwości będzie biegł ścieżką o najmniejszej impedancji. Droga prądu powrotnego będzie biegła tuż pod ścieżka prowadzącą sygnał pierwotny.

Złe zaprojektowanie ścieżki dla prądu zwrotnego może doprowadzić do utworzenia dużej pętli prądowej, mającej tendencje do zbierania szumu elektromagnetycznego oraz do jego generacji. Należy też zwrócić uwagę na fakt, że ścieżki dla wolnych przebiegów analogowych i szybkich cyfrowych będą wyglądały inaczej. Wniosek z tego jest prosty: skoro są inne, to nie będą się zakłócać.

W związku z powyższym, przynajmniej jedna warstwa powinna zostać w całości poświęcona na płaszczyznę masy. Wszelkie nieciągłości w płaszczyźnie masy mogą spowodować zakłócenie ścieżek prądów zwrotnych. Z tego właśnie powodu niekorzystne jest dzielenie masy. Poprowadzenie sygnału o wysokiej częstotliwości nad granicą między powierzchniami masy może doprowadzić do powstania dużej pętli prądowej. Jeżeli podział mas jest niezbędny, to należy dokładnie zbadać czy nie zostaną zakłócone ścieżki prądów zwrotnych. W wypadku prowadzenia linii sygnałowych między masami, muszą one przebiegać nad mostkiem łączącym obie masy.

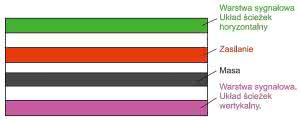

W płytkach wielowarstowych (gdzie liczba warstw jest większa od dwóch) przynajmniej jedna warstwa powinna być przeznaczona na płaszczyznę masy. Każda z warstw sygnałowych musi znajdować się w sąsiedztwie płaszczyzny masy, ewentualnie płaszczyzny zasilania, w celu zapewnienia niskoimpedancyjnej ścieżki prądu zwrotnego.

Rysunek 2. Ułożenie warstw w płytkach 4-warstowych. Jest pożądane, aby warstwy sygnałowe były jak najbliżej płaszczyzny masy bądź zasilania

W przypadku płytek 4-warstowych najlepiej, aby płaszczyzna masy znajdowała się na jednej z wewnętrznych warstw (rysunek 2). Drugą, wewnętrzną warstwę warto w całości przeznaczyć na płaszczyznę zasilającą. Sprawi to, że pomiędzy nimi utworzony zostanie kondensator odsprzęgający warstwę zasilającą.

Dodatkowo, w celu zmniejszenia oddziaływania elektromagnetycznego między warstwami sygnałowymi warto, aby ścieżki na sąsiednich warstwach przebiegały względem siebie pod kątem prostym. Możliwym rozwiązaniem jest również utworzenie płaszczyzn masy na dwóch zewnętrznych warstwach, oraz rozprowadzenie ścieżek sygnałowych i zasilania na wewnętrznych.

To rozwiązanie jest gorsze od poprzedniego, ponieważ sprawia, że wprowadzenie jakichkolwiek zmian w projekcie mozaiki połączeń jest trudniejsze. Dodatkowo, jeżeli na płytce mają się znaleźć elementy dyskretne, to muszą zostać umieszczone na zewnętrznej warstwie, więc ciągłość jednej z płaszczyzn zostanie naruszona. Wpłynie to niekorzystnie na jej właściwości.

Podobnie należy postąpić przy wykonywaniu projektu płytki 6-warstwowej (rysunek 3). Jedyną różnicą jest niemożność umieszczenia w bezpośrednim sąsiedztwie warstwy zasilającej i masy, a więc utrata niskoimpedancyjnego połączenia między nimi. Można to łatwo zrekompensować dodając pomiędzy nimi kondensatory ceramiczne o niewielkiej pojemności.

Tutaj dojdzie do sytuacji, w której dwie warstwy sygnałowe będą ze sobą sąsiadowały. Należy tutaj bezwzględnie trzymać się zasady, aby ścieżki na danej warstwie były prowadzone prostopadle względem ścieżek biegnących na sąsiedniej warstwie sygnałowej. Płaszczyzny masy i zasilania powinny oddzielać od siebie warstwy, na których prowadzone są szybkie sygnały cyfrowe od warstw z wrażliwymi sygnałami analogowymi.

Najtrudniejsze do zaprojektowania pod względem EMC są jednak systemy oparte na płytkach 1- i 2-warstwowych. O ile w pierwszym wypadku nie zawsze można sobie pozwolić na poświęcenie jednej warstwy na powierzchnie masy, to już w drugim jest to w ogóle niemożliwe. Projektując urządzenie elektroniczne na płytce 1-warstwowej można bardzo łatwo utworzyć dużą pętlę prądu zwrotnego.

Ten problem może zostać rozwiązany poprzez użycie przelotek czy dodatkowych przewodów. Co prawda tak wykonany "pająk" nie będzie zbyt estetyczny, ale nie o to tutaj chodzi. Najlepszym rozwiązaniem jest przeniesienie tego projektu na płytkę 2-warstwową i przeznaczenie jednej warstwy na masę. Wzrost kosztów produkcji będzie niewielki, a poprawa parametrów znaczna.

Wróćmy do płytek 2-warstwowych. Nie zawsze można pozwolić sobie na poświęcenie całej powierzchni na masę, ale jest na to lekarstwo. Nazywa się ono: siatką masy. Nie jest ona tak dobra, jak ciągła płaszczyzna masy, ale zawsze jest dużo lepsza niż jej brak i rozprowadzenie masy ścieżkami. Ważnym parametrem siatki masy jest wielkość oczek oraz szerokość ścieżek ją tworzących.

Od nich zależy jej indukcyjność (im mniejsza, tym lepiej). Ścieżki powinny być jak najszersze, a oczka jak najmniejsze. Generalnie oczka nie powinny być większe niż 8 mm. Idealna siatka masy jest utworzono ze ścieżek ułożonych poziomo na jednej warstwie i pionowo na drugiej (między nimi jest zachowany kąt prosty). W obrębie warstwy, ścieżki masy powinny być do siebie równoległe.

W miejscach skrzyżowania ścieżek masy, będących na sąsiednich warstwach należy umieścić przelotki. W celu obniżenia impedancji połączenia, można tam też umieścić kondensator odsprzęgający. Po przygotowaniu siatki można przystąpić do umieszczenia na płytce elementów oraz rozprowadzić ścieżki zasilania i sygnałowe. Nie można usuwać segmentów siatki masy.

Jeżeli w miejscu jego występowania chcielibyśmy umieścić ścieżkę albo element, musimy oczko przenieść na drugą stronę płytki. Przelotki można usunąć, jeżeli nie są potrzebne. W ten sam sposób można wykonać również siatkę zasilania. Należy wtedy ścieżki zasilania prowadzić równolegle do ścieżek masy, w celu zapewnienia niskoimpedancyjnego połączenia między nimi(zwierającego sygnały szybkozmienne).

Oprócz utworzenia płaszczyzny masy, konieczne jest również umieszczenie ścieżek oraz pól masy na warstwie/warstwach sygnałowych. Ich zadaniem jest zapobiegnięcie rozprzestrzeniania się szumu elektromagnetycznego o wysokiej częstotliwości na sąsiednie ścieżki i elementy.

Prowadząc ścieżkę masy warto trzymać się zasady, aby stosunek jej długości do szerokości był co najwyżej jak 10:1 (jeżeli będzie wyższy, należy dodać kolejne przelotki łączące ją z płaszczyzną masy) oraz aby na obu jej końcach znajdowały się przelotki łączące ją z płaszczyzną masy.

Ścieżki masy powinny:

- być umieszczone pomiędzy ścieżkami prowadzącymi sygnały szybko zmienne, a pozostałymi ( w tym zasilania) w celu zapobiegnięcia wyindukowaniu niechcianego prądu na innych liniach;

- warto umieszczać linie masy w sąsiedztwie linii prowadzących sygnały krytyczne (tj. mocno szumiące, bądź bardzo wrażliwe) i zasilanie;

- w przypadku tworzenia magistrali cyfrowej, w sąsiedztwie masy powinno się znajdować co najwyżej 8 linii, w bezpośrednim sąsiedztwie najlepiej aby znajdowała się linia odpowiedzialna za przesyłanie sygnału zegarowego, bądź stanu najmłodszego bitu adresu/danych. Powodem tego jest to, że stan tej linii zmienia się z największą częstotliwością, a więc generuje ona najwięcej szumu.

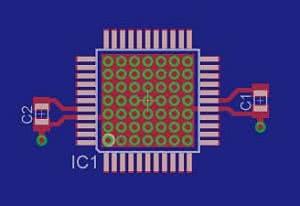

Rysunek 5. Sposób podłączenia kondensatorów odsprzęgających oraz dodatkowa powierzchnia masy umieszczona bezpośrednio pod układem scalonym

W celu zmniejszenia emisyjności układów wysokoszumnych (np. oscylatorów, układów cyfrowych) zaleca się umieszczanie pod nimi placków miedź połączonych jak największą liczbą przelotek z płaszczyzną masy (rysunek 5). Poprawia to również odprowadzanie ciepła z układu. Pola masy powinny być połączone z wyprowadzeniami masy z układu.

Projekt zasilania układu. Z punktu widzenia kompatybilności elektromagnetycznej bardzo istotne jest przyłożenie się do projektu zasilania. Nie należy lekceważyć tego zadania, ponieważ wszelkie zaniedbania na tym polu mogą wpłynąć niekorzystnie na stabilność napięcia zasilającego. Zmiany wartości napięcia zasilającego wpłyną szczególnie niekorzystnie na wrażliwe obwody analogowe oraz pracę przetworników A/C i C/A.

Przy projektowaniu zasilania systemu, w którym są wykorzystywane układy cyfrowe jest często popełniany dość poważny błąd. Pobór prądu podany w nocie katalogowej tego rodzaju przyrządów jest w istocie wartością skuteczną. Układy cyfrowe pobierają prąd podczas pojawienia się zbocza sygnału zegarowego, w postaci wąskich i wysokich (czasami o wartości setek mA) pików.

Jak już wcześniej wspomniałem prądy o dużym natężeniu i wysokiej częstotliwości (wąski pik w dziedzinie częstotliwości jest widziany jako zbiór wysokoczęstotliwościowych sinusoid) wytwarza wokół przewodnika w którym płynie silne pole magnetyczne, które to z kolei powoduje wyindukowanie niepożądanej siły elektromotorycznej na sąsiednich ścieżkach.

Ratunkiem jest jak najwcześniejsze zwarcie takiego piku do masy, przez użycie kondensatora odsprzęgającego (przynajmniej jednego), umieszczonego jak najbliżej doprowadzenia zasilania układu cyfrowego. Użycie większej ilości kondensatorów polepszy rezultaty odsprzęgania. Dobierając kondensator odsprzęgający należy kierować się częstotliwością samorezonansu (tabela 1).

Im wyższa, tym szybsze sygnały może zewrzeć do masy. Jego pojemność ma drugorzędne znaczenie. Najlepszym wyborem będzie wielowarstwowy kondensator ceramiczny. Taki kondensator (przynajmniej jeden) powinien pojawić się przy wszystkich doprowadzeniach zasilających. Druga okładka kondensatora powinna być dołączona do najbliższego wyprowadzenia masy układu i zwarta przelotką do płaszczyzny masy.

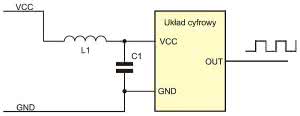

Rysunek 6. Podłączenie kondensatora odsprzęgającego C1 blisko pinu zasilającego w celu uzyskania małej pętli dla prądu zwrotnego. Układ podłączono z szyną zasilającą przez cewkę ferrytową L1 w celu zapobiegnięcia przeniesienia szumu wysokoczęstotliwościowego na szynę zasilania

Aby dodatkowo zminimalizować propagację tętnień na linię zasilającą, można dołączyć do niej zasilanie układu cyfrowego za pośrednictwem dławika (rysunek 6). Przy wyborze cewki najważniejszym parametrem jest niska rezystancja. Najlepszym wyborem w tej kwestii są cewki ferrytowe. Cechują się one bardzo niską rezystancją dla prądów stałych, natomiast dla sygnałów o wysokiej częstotliwości ich impedancja jest bardzo wysoka.

Oprócz wystąpienia EMI, taki sposób pobierania prądu może spowodować również obniżenie napięcia na szynie zasilającej. Jest to wynikiem ograniczonej wydolności prądowej rzeczywistych układów zasilających. W celu uniknięcia takiej sytuacji należy na wyjściu podsystemu zasilającego umieścić duży kondensator elektrolityczny. Będzie spełniał on rolę rezerwuaru energii.

Istotnym parametrem jest jego pojemność. Praktyczna zasada mówi, że jego pojemność powinna być przynajmniej 10 razy większa, niż suma pojemności kondensatorów odsprzęgających podpiętych do linii zasilania. Jako, że elektrolity mają niską częstotliwość samorezonansu, a co za tym idzie kiepsko zwierają wąskie piki prądowe do masy, należy wpiąć równolegle kondensator odsprzęgający.

Szyna zasilająca musi być bezwzględnie chroniona przed przepięciami. Źródłem skoku napięcia może być pobliskie wyładowanie elektrostatyczne, bądź interferencja elektromagnetyczna. Remedium na to zjawisko jest wpięcie w kierunku zaporowym diody Zenera pomiędzy linie zasilającą, a masę (rysunek 7).

Po przekroczeniu napięcia Zenera gwałtownie rośnie natężenie przewodzonego przez nią prądu. Napięcie Zenera w niewielkim stopniu zależy od natężenia przepływającego prądu. W efekcie nadmiar ładunku zostaje błyskawicznie odprowadzony, a napięcie zasilania systemu nie będzie wyższe niż napięcie Zenera.

Trzeba dobrać diodę Zenera w zależności od nominalnego napięcia zasilającego oraz zakresu napięcia, jakie może zostać doprowadzone do użytych układów. Generalnie, napięcie Zenera powinno być nieco wyższe od nominalnego napięcia zasilającego.

Dlaczego nie powinno się użyć diody o wartości napięcia Zenera równemu napięciu nominalnemu zasilania? Otóż, diody Zenera nie są elementami idealnymi. Napięcie przebicia jest podawane z pewną tolerancja. Na domiar złego zależy ono od temperatury złącza p-n.

Jeżeli napięcie Zenera spadłoby poniżej nominalnego napięcia zasilania, to okazałoby się, że napięcie zasilania również spadło (w wyniku ograniczonej wydolności prądowej układu zasilania) oraz część energii zamiast trafić do układów, została by rozproszona w postaci promieniowania podczerwonego.

Rozmieszczając elementy układu zasilającego na płytce PCB warto zadbać o to, aby zajmował on jak najmniejszą powierzchnię. Uniknie się w ten sposób utworzenia dużych pętli prądów zwrotnych, które będą emitowały i odbierały zakłócenia elektromagnetyczne.

Jeżeli system jest wykonywany na płytkach co najmniej 4-warstowych, należy przeznaczyć jedną warstwę w całości na płaszczyznę zasilania. W celu zapewnienia niskoimpedancyjnej ścieżki dla prądów zwrotnych płaszczyzna ta powinna znajdować się w bezpośrednim sąsiedztwie płaszczyzny masy. Jeżeli jest to z jakiegoś powodu niekorzystne, należy wtedy zapewnić niskoimpedancyjne połączenie między nimi, przy pomocy równomiernie rozłożonych kondensatorów odsprzęgających.

W płytkach o mniejszej liczbie warstw, gdzie nie ma możliwości przeznaczenia jednej warstwy na zasilanie, to do zadania rozprowadzenia ścieżek zasilających można podejść w dwojaki sposób. Pierwszym z nich jest stworzenie siatki zasilania na wzór siatki masy. W celu zapewnienia jak najlepszego odprowadzania szumów wysokoczęstotliwościowych, ścieżki zasilania powinny biec równolegle do ścieżek masy.

Drugim sposobem jest rozprowadzenie zasilania za pomocą ścieżek. Podobnie jak w wypadku siatki zasilania: pod nimi, albo w ich bezpośrednim sąsiedztwie powinny biec równolegle ścieżki masy. W pobliżu linii zasilających nie mogą znajdować się elementy i ścieżki wysok oszumne (zwłaszcza, kiedy biegną one równolegle).

Może to doprowadzić do zaburzenia napięcia zasilającego i w efekcie niepoprawnej pracy układu. Zasilanie należy prowadzić jak najkrótszymi (o długości mniejszej niż l/20 najkrótszej fali spodziewanego zakłócenia) i najgrubszymi ścieżkami. Najlepiej, aby nie został przekroczony stosunek długości do szerokości 10:1. W celu zminimalizowania wpływu poszczególnych układów na siebie, linie zasilające dla każdego układ powinny zaczynać się w jednym punkcie. Najlepiej w miejscu podłączenia kondensatora magazynującego energię.

Podsumowanie

Wykonanie systemu spełniającego założenia kompatybilności elektromagnetycznej nie musi być ani trudne, ani drogie. Wystarczy przyjrzeć się zjawisku interferencji elektromagnetycznej z bliska i wyeliminować potencjalne źródła kłopotów.

Rafał Łaziński

r@lazinski.pl

Zaloguj

Zaloguj